13.7. Techniques for Improving Performance

Several practical methods can be used to improve the performance of switching systems. The enhancement of a switch performance is typically related to speed, throughput, and therefore the possibility of blocking. Some possible methods for enhancing performance in switching systems are as follows :

-

Buffering. The use of buffers in switching networks reduces traffic congestion and thus increases system throughput. With the use of buffers in a switch, packets are not discarded when they request the same switch output but instead are kept in buffers for a later contention resolution.

-

Combined networks. Combined networks consists of several cascaded switch fabrics , providing extra stages and producing extra paths, although a combined network can also be designed for other purposes, such as multicasting.

-

Randomizing traffic. This technique is used to distribute traffic evenly across the switching network to prevent local congestion.

-

Recirculation of traffic. A packet that is not successfully delivered to a given port can be recirculated. Such packets contend for deliverypossibly with higher prioritiesin the next cycle.

-

Increase speed-up factor. This speed advantage in a switching system refers to the ratio of the internal link speed to the external link speed.

-

Parallel-plane switching networks. This technique forms parallel planes of switch fabrics to process slices of a packet in parallel.

The use of buffering, combined networks, and parallel-plane switching networks results in increased system complexity and cost but also better performance. Let's take a look at one such technique.

13.7.1. Parallel-Plane Switching Networks

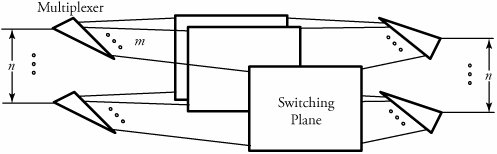

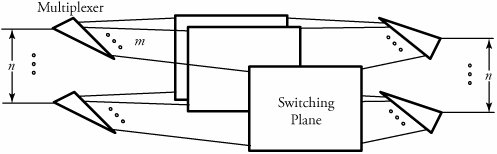

One possible way to improve the performance and speed of switching networks, especially to reduce the blocking probability, is to arrange parallel planes, or slices, of the switching network, as shown in Figure 13.12. The Cantor network , K n,d,k , is a widely used example of parallel-plane networks and is constructed by m planes of Bene  switching networks, B n , d . The Cantor network is defined by

switching networks, B n , d . The Cantor network is defined by

Equation 13.18

Figure 13.12. A Cantor network with m parallel switching planes for better reliability

The Cantor network is strictly nonblocking whenever

Equation 13.19

For d = 2, this reduces to m  log 2 n , which gives us a strictly nonblocking network with approximately 4 n( log 2 n ) 2 crosspoints.

log 2 n , which gives us a strictly nonblocking network with approximately 4 n( log 2 n ) 2 crosspoints.

| |

| Example. | For n = 2 12 , compare crossbar, Clos network, and Cantor network complexities. |

| Solution. | If n = 2 12 , the complexity for a crossbar is n 2 = 2 24  17 x 10 6 . For a Clos network, the complexity is . For a Cantor network, the complexity is 4 n( log n ) 2 = 2 24 = 2.4 x 10 6 . 17 x 10 6 . For a Clos network, the complexity is . For a Cantor network, the complexity is 4 n( log n ) 2 = 2 24 = 2.4 x 10 6 . |

In parallel-plane switching networks, the chip pin constraint limits the number of signals that can enter or leave a physical component. The integrated circuit pin constraints also influence implementation so that such systems are best designed with each data path passing through physically separate components . Such bit-sliced organization causes complexity to grow in proportion to the data path width.

switching networks,

switching networks,

log 2

log 2  17 x 10 6 . For a Clos network, the complexity is . For a Cantor network, the complexity is 4

17 x 10 6 . For a Clos network, the complexity is . For a Cantor network, the complexity is 4