System Management Mode (SMI SMIACT)

System Management Mode (SMI# & SMIACT#)System Management Mode (SMM) is a special mode of operation supported by x86 microprocessors in addition to their real and protected modes of operation. SMM was introduced originally to support power management in mobile PCs. Today power management is largely handled by the operating system (O.S.), but SMM is still used in a variety of other applications. SMM ApplicationsSystem management mode (SMM) allows the processor to execute code from system management memory that is separate from the regular memory used by the operating system and applications. This permits the system designer to implement features that are transparent to the operating system, making SMM extremely valuable for applications not supported by the O.S., or where O.S. transparency is important. Some example applications are:

The HT specification supports SMM by permitting HT devices to generate a system management interrupt (SMI), which puts the processor into SMM. This type of action is common to a south bridge or I/O Controller Hub in an x86-based system (e.g. USB support). The HT specification expressly prohibits any HT device other than the ICH/South bridge from sending an SMI Request message. Legacy SMM SignalsThe x86 processors implement two signals to support SMM.

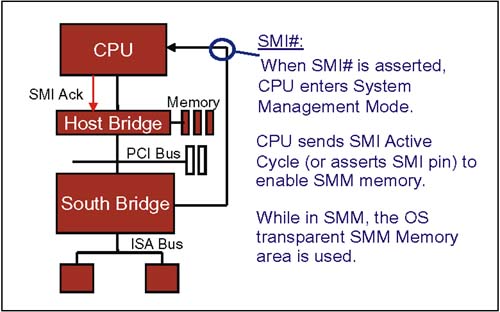

Figure 22-16 on page 513 illustrates SMM signaling in a legacy system. The system management interrupt (SMI#) causes the processor to enter system management mode. When SMI# is recognized asserted on an instruction boundary, it completes all buffered write transactions, and signals SMI acknowledge (SMIACT#). The processor then saves the contents of its internal registers to system management RAM (SMRAM) and begins to fetch and execute SMM code. Figure 22-16. SMM Signaling in Legacy Systems The HT Method of Signaling SMI# & SMIACT#HT conveys SMI# to the Host Bridge via an SM interrupt message cycle. The bridge in turn asserts the SMI# signal to the processor, or optionally can send the SMI# request via the APIC bus in a multiprocessor environment. An x86 processor responds with an SMI Active indication using one of two possible methods depending on the model:

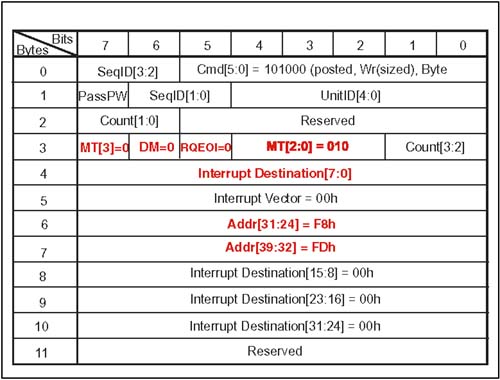

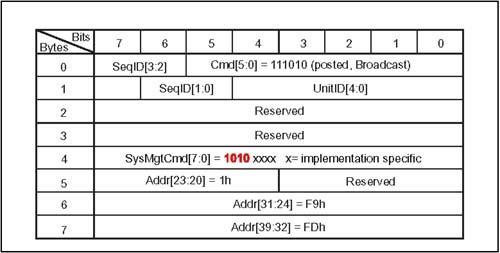

In either case, the Host Bridge broadcasts the SMIACT indication to the SMC via an HT special cycle. Figure 22-17 on page 514 illustrates the contents of the Interrupt Request packet that the SMC uses when signaling SMI, and Figure 22-18 on page 515 illustrates the SM Request packet contents that the Host Bridge broadcasts when signaling SMIACT. Figure 22-17. SM Request Content for SMI Message Figure 22-18. SM Message Content for SMIACT |

EAN: 2147483647

Pages: 182