Section 5.1. How Hardware Does It: Busses, Bridges, Ports, and Interfaces

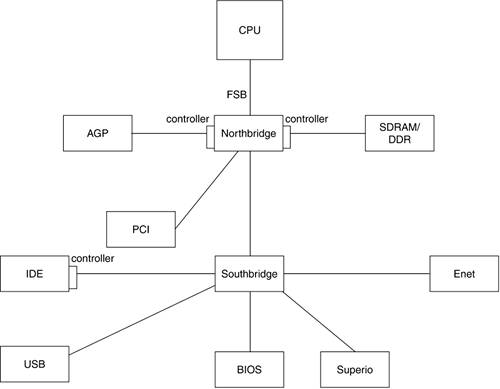

5.1. How Hardware Does It: Busses, Bridges, Ports, and InterfacesThe way a processor communicates with its surrounding devices is through a series of electrical connections, or lines. Busses are groups of these lines with similar function. The most common types of busses going to and from a processor are used for addressing the devices; for sending and receiving data from the devices; and for transmitting control information, such as device-specific initialization and characteristics. Thus, we can say the principal method for a device to communicate with the processor (and vice versa) is through its address bus, data bus, and control bus. The most basic function of a processor in a system is to fetch and execute instructions. These instructions are collectively called a computer program or software. A program resides in a device (or group of devices) known as memory. The processor is attached to memory by way of the address, data, and control busses. When executing a program, the processor selects the location of an instruction in memory by way of the address bus and transfers (fetches) the instruction by way of the data bus. The control bus handles the direction (in or out of the processor) and type (in this case, memory) of transfer. Possibly adding to the confusion in this terminology is that, when we refer to a particular bus, such as the front-side bus or the PCI bus, we mean the address, data, and control busses all together. The task of running software on a system requires a wide array of peripheral devices. Recent computer systems have two major peripheral devices (also called controllers), which are referred to as the Northbridge and the Southbridge. Traditionally, the term bridge describes a hardware device that connects two busses. Figure 5.1 illustrates how the Northbridge and the Southbridge interconnect other devices. Collectively, these controllers are the chipset of the system. Figure 5.1. Old Intel

The Northbridge connects the high-speed, high-performance peripherals, such as the memory controller and the PCI controller. While there are chipset designs with graphics controllers integrated into the Northbridge, most recent designs include a high-performance bus, such as the Accelerated Graphics Port (AGP) or the PCI Express, to communicate with a dedicated graphics adaptor. To achieve speed and good performance, the Northbridge bridges the front-side bus[1] with, depending on the particular chipset design, the PCI bus and/or the memory bus.

The Southbridge, which connects to the Northbridge, is also connected to a combination of low-performance devices. The Intel PIIX4, for example, has its Southbridge connected to the PCI-ISA bridge, the IDE controller, the USB, the real-time clock, the dual 82C59 interrupt controller (which is covered in Chapter 3, "Processes: The Principal Model of Execution"), the 82C54 timer, the dual 82C37 DMA controllers, and the I/O APIC support. In the earliest x86-based personal computers, communication with basic peripherals, such as the keyboard, the serial port, and the parallel port, was done over an I/O bus. The I/O bus is a type of the control bus. The I/O bus is a relatively slow method of communication that controls peripherals. The x86 architecture has special I/O instructions, such as inb (read in a byte) and outb (write out a byte), which communicate over the I/O bus. The I/O bus is implemented by sharing the processor address and data lines. Control lines activated only when using the special I/O instructions prevented I/O devices from being confused with memory. The PowerPC architecture has a different method of controlling peripheral devices; it is known as memory-mapped I/O. With memory-mapped I/O, devices are assigned regions of address space for communication and control. For example, in x86 architecture the first parallel port data register is located at I/O port 0x378, whereas in the PPC it could be, depending on the implementation, at memory location 0xf0000300. To read the first parallel port data register in x86, we execute the assembler instruction in al, 0x378. In this case, we activate a control line to the parallel port controller. This indicates to the bus that 0x378 is not a memory address but an I/O port. To read the first parallel port data register in PPC, we execute the assembly instruction lbz r3, 0(0xf0000300). The parallel port controller watches the address bus[2] and replies only to requests on a specific address range under which 0xf0000300 would fall.

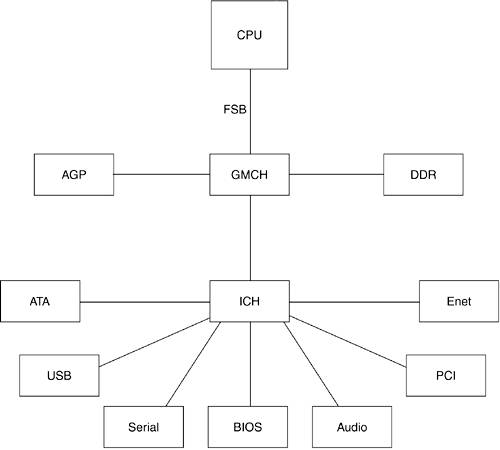

As personal computers matured, more discrete I/O devices were consolidated into single integrated circuits called Superio chips. Superio function is often further consolidated into a Southbridge chip (as in the ALI M1543C). As an example of typical functionality found in a discrete Superio device, let's look at the SMSC FDC37C932. It includes a keyboard controller, a real-time clock, power management device, a floppy disk controller, serial port controllers, parallel ports, an IDE interface, and general purpose I/O. Other Southbridge chips contain integrated LAN controllers, PCI Express controllers, audio controllers, and the like. The newer Intel system architecture has moved to the concept of hubs. The Northbridge is now known as the Graphics and Memory Controller Hub (GMCH). It supports a high-performance AGP and DDR memory controller. With PCI Express, Intel chipsets are moving to a Memory Controller Hub (MCH) for graphics and a DDR2 memory controller. The Southbridge is known as the I/O Controller Hub (ICH). These hubs are connected through a proprietary point-to-point bus called the Intel Hub Architecture (IHA). For more information, see the Intel chipset datasheets for the 865G[3] and the 925XE.[4] Figure 5.2 illustrates the ICH.

Figure 5.2. New Intel Hub

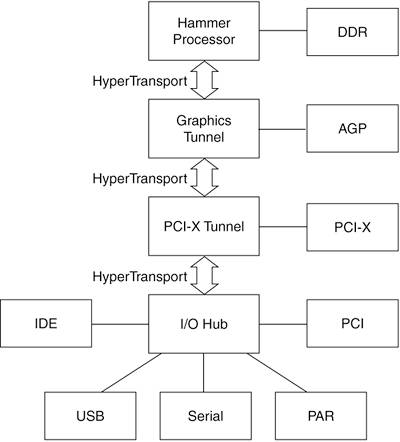

AMD has moved from the older Intel style of the Northbridge/Southbridge to the packetized HyperTransport technology between its major chipset components. To the operating system, HyperTransport is PCI compatible.[5] See AMD chipset datasheets for the 8000 Series chipsets. Figure 5.3 illustrates the HyperTransport technology.

Figure 5.3. AMD HyperTransport

Apple, using the PowerPC, has a proprietary design called the Universal Motherboard Architecture (UMA). UMA's goal is to use the same chipset across all Mac systems. The G4 chipset includes the "UniNorth memory controller and PCI bus bridge" as a Northbridge and the "Key Largo I/O and disk-device controller" as a Southbridge. The UniNorth supports SDRAM, Ethernet, and AGP. The Key Largo Southbridge, connected to the UniNorth by a PCI-to-PCI bridge, supports the ATA busses, USB, wireless LAN (WLAN), and sound. The G5 chipset includes a system controller Application Specific Integrated Circuit (ASIC), which supports AGP and DDR memory. Connected to the system controller via a HyperTransport bus is a PCI-X controller and a high-performance I/O device. For more information on this architecture, see the Apple developer pages. By having this brief overview of the basic architecture of a system, we can now focus on the interface to these devices provided by the kernel. Chapter 1, "Overview," mentioned that devices are represented as files in the filesystem. File permissions, modes, and filesystem-related system calls, such as open() or read(), apply to these special files as they do to regular files. The significance of each call varies with respect to the device being handled and is customized to handle each type of device. In this way, the details of the device handling are made transparent to the application programmer and are hidden in the kernel. Suffice it to say that when a process applies one of the system calls on the device file, it translates to some kind of device-handling function. These handling functions are defined in the device driver. We now look at the types of devices. |

EAN: N/A

Pages: 134