PowerTheater Designer

The PowerTheater Designer product uses Watt Watcher's proven RTL estimation technology to build a detailed, quantitative map of the power in the design. PowerTheater Designer then invokes a suite of patent-pending agents called WattBots that automatically measure the impact of many potential power-saving architectural changes. Each WattBot is designed to identify a specific type of power reduction opportunity. The suite of WattBots covers all major types of circuitry in the design, including control, datapath, I/O, memory, and clocks. For each opportunity identified, PowerTheater Designer proposes specific RTL design modifications and quantifies the power savings that would result, together with certain potential trade-offs, such as any area penalty. Users then choose which changes to implement and which to reject, based on their power targets and design flow needs.

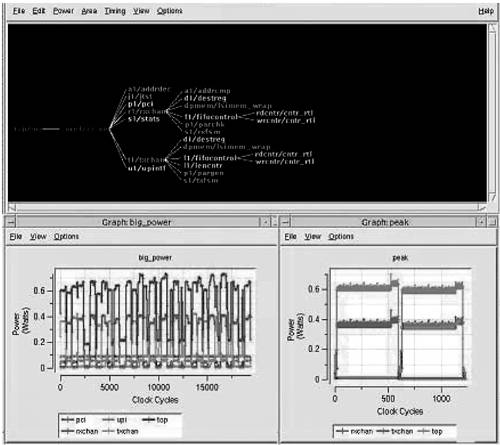

Figure A.3. PowerTheater Designer's Graphical User Interface

PowerTheater Designer operates at the RT level and locates much larger power reductions than are available via gate-level techniques such as local clock gating and buffer resizing.

Features and Benefits

-

RTL power reduction for system-on-a-chip integrated circuits

-

Allows presynthesis optimization covering all major contributors of power dissipation:

memory

clocks

data paths

control logic

I/O

-

20 “40% power reduction on large ICs, vs. 5 “10% for gate/synthesis-based tools

-

Supports both Verilog and VHDL languages

-

Versatile graphical analysis environment lets designers assess trade-off options quickly

| |

| |

| Top |

EAN: 2147483647

Pages: 61