IO Address ReMapping

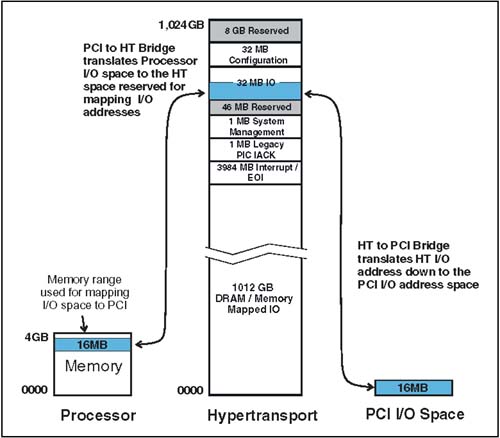

I/O Address ReMappingBecause HT does not directly support I/O address space, it reserves a 32MB of memory address space for transporting I/O addresses across the bus. When the processor initiates and I/O transaction, the address must be translated by the CPU to HT bridge to an address within the reserved HT I/O address range (FD_FC00_0000h- FD_FDFF_FFFFh). HT transports the transaction across the HT chain to the HT-to-PCI bridge which must translate the HT I/O address so that is falls within the expansion bus I/O address range. The IO Size register within the Address Remapping Capability block supports the I/O address space remapping. This 5-bit register defines the size of the I/O address space on the expansion bus, up to 32MBs. Note that the upper 15 bits of the HT I/O address range (FD_FC00_0000h- FD_FDFF_FFFFh) identifies the address as I/O, while the lower 25 address bits define any location within the 32MB I/O address range. The I/O Size register specifies the number of upper address bits (Addr 24:0) that will not be used when generating an I/O address on the expansion bus. For example, an I/O size value of 01101b (13d) results in an expansion bus I/O range of 4KB (Addr 11:0). The default value of zero causes all 25 bits of a HyperTransport I/O request to be passed to the expansion bus, thereby supporting the maximum 32MB I/O range. The next two sections give example implementation of I/O address remapping. X86 Processor and PCI I/O Remapping ExampleThis example assumes that the x86 processor and the PCI bus support a maximum I/O address space of 64KB as illustrated in Figure 21-3 on page 483. The Host to HT bridge translates each processor initiated I/O address up to the reserved HT I/O address range and the HT-to-PCI bridge translates the address back down to the PCI I/O address range. HT-to-PCI bridges use the PCI to PCI bridge's I/O Base and Limit configuration registers that are defined by the PCI 2.3 and earlier specifications, along with the I/O size field of the Address Remapping capability block. Figure 21-3. X86 Processor I/O Mapping Example In this example, the processor performs a read from I/O address 058Ah that targets a location within a PCI device. The following actions are taken:

PowerPC and PCI I/O Remapping ExampleSome processors such as the PowerPC may not support I/O address space. In this case, the CPU to HT bridge must translate a range of processor memory address space to the HT I/O address range. The translation from HT-to-PCI I/O address space is accomplished using the I/O Size field of the Address Remapping capability block. In this example, a 16MB block of processor memory space is dedicated for I/O address mapping. Consequently, the PCI can support up to 16MB of I/O space that can be accessed by software executing on the CPU. Figure 21-4 on page 484 illustrates this address remapping. The I/O Size value in this example would be 00001b to indicate that only the upper address bit of the 24-bit I/O address will be ignored, yielding a valid PCI I/O address of Addr[23:0]. Figure 21-4. PowerPC I/O Mapping Example |

EAN: 2147483647

Pages: 182