Signaling Wakeup

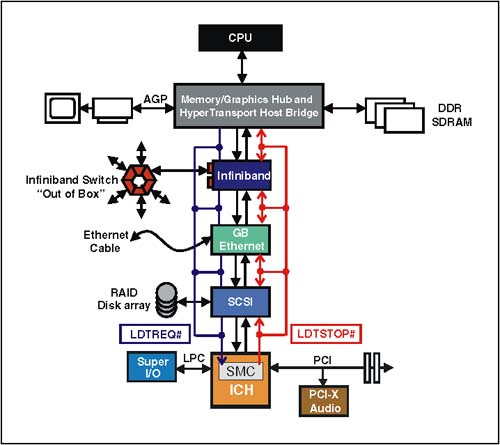

Signaling WakeupMost power management schemes provide a mechanism that allows a device to initiate a sequence that returns the system from a power conservation state to a fully operational state. HT provides this ability via the LDTREQ# signal. Figure 18-2 shows that the LDTREQ# signal is an output from each HT device interface and an input to the SMC. Figure 18-2. LDTREQ# is an Output from All HT Devices and an Input to the SMC. An HT device currently in a low-power state (LDTSTOP# asserted) may assert LDTREQ# to initiate a system wakeup. The actions taken by the SMC to transition the system back to normal operation includes:

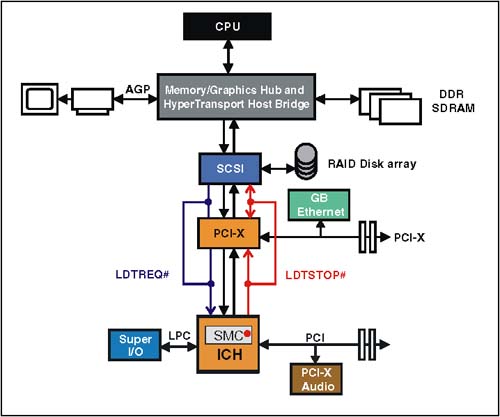

A HT device that might be required to implement LDTREQ# is an HT-to-PCI-X bridge. See Figure 18-3. PCI-X requires support for power management, including the possibility of a PCI-X device signaling a wakeup event via the SME# (System Management Event) signal. The assertion of SME# is intended to awaken the system, and in an HT platform this is accomplished via LDTREQ#. Note that if the HT SMC is located within the PCI-X bridge, then the SMC would simply deassert LDTSTOP# to initiate the system wakeup. Figure 18-3. Example Wakeup Signaled by HT-to-PCI-X Bridge. |

EAN: 2147483647

Pages: 182