4.5 FPMA and SoPC

|

4.5 FPMA and SoPC

Today's electronic systems are very complex and include digital logic, interfacing as well as analogue circuits. Eventually, such mixed-signal systems will be integrated on a single programmable chip. This section introduces the relevant FPMA, SoC and SoPC concepts and systems.

4.5.1 FPMA

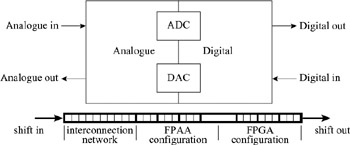

An FPMA is an integrated circuit containing both an FPGA and an FPAA, connected through configurable signal converters as shown in Figure 4.15. The FPMA is a hybrid chip combining analogue and digital cells. The digital cells are standard FPGA circuits, while the analogue cells constitute a standard FPAA [26].

Figure 4.15: Generic FPMA

4.5.2 SoC and SoPC

The concept of systems on a single chip is not new and for years researchers have been trying to implement a whole application on a single piece of silicon. The implementation of different parts of the application on a single chip is known as system on a chip (SoC). There are quite a few reasons for implementing the SoC concept. These include: increased system performance, reduced system power dissipation, reduced product cost, smaller system size, and system consideration. The disadvantages of SoC are higher development cost and time. This could be solved by introducing the SoPC (system on a programmable chip). The concept of SoPC is developing a complete solution for any kind of system. The SoPC may contain both the FPAA and FPGA, which is similar to the FPMA. The future reconfigurable universal transceiver should ideally be a SoPC device. But unfortunately to implement this kind of universal SoPC with CMOS only is very difficult and there have hardly been any commercial products available. The SoPC from Altera is restricted to digital circuits only [27].

4.5.3 Commercial mixed-signal SoPC: SIDSA FIPSOC

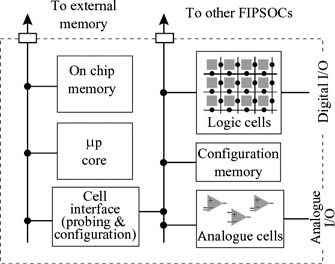

FIPSOC (FIeld-Programmable System-On-a-Chip) provides the user with the possibility of integrating a microprocessor core along with programmable digital and analogue cells within the same integrated circuit [26]. This chip can be considered as a large granularity FPGA (logic cells) with a FPAA (analogue cells) and a built-in microprocessor core (8051) that not only acts as a general-purpose processing element, but also configures the programmable cells and their interconnections. Therefore, there is an interaction between hardware and software as long as signal values and configuration data within the programmable cells are accessible from the element of the FPGA. The block diagram of the FIPSOC is shown in Figure 4.16 [26]. The FPAA is for signal conditioning and uses the continuous-time circuit techniques. Configurable converter blocks produce 8–10 bits resolution.

Figure 4.16: Block diagram of FIPSOC

|

EAN: 2147483647

Pages: 100